# Implementation Of Grigoryan FFT For Its Performance Case Study Over Cooley-Tukey FFT Using Xilinx Virtex-II Pro, Virtex-5 And Virtex-4 FPGAs

Narayanam Ranganadh<sup>1</sup>, Muni Guravaiah P<sup>2</sup>, Bindu Tushara D<sup>3</sup>

<sup>1</sup>Department of Electronics and Communications Engineering, Bharat Institute of Engineering and Technology, Hyderabad, A.P., India.

rnara100@uottawa.ca,rnara100@biet.ac.in,rnara100@gmail.com

#### ABSTRACT

A large family of signal processing techniques consist of Fourier-transforming a signal, manipulating the Fourier-transformed data in a simple way, and reversing the transformation. We widely use Fourier frequency analysis in equalization of audio recordings, X-ray crystallography, artefact removal in Neurological signal and image processing, Voice Activity Detection in Brain stem speech evoked potentials, speech processing spectrograms are used to identify phonetic sounds and so on. Discrete Fourier Transform (DFT) is a principal mathematical method for the frequency analysis. The way of splitting the DFT gives out various fast algorithms. In this paper, we present the implementation of two fast algorithms for the DFT for evaluating their performance. One of them is the popular radix-2 Cooley-Tukey fast Fourier transform algorithm (FFT) [1] and the other one is the Grigoryan FFT based on the splitting by the paired transform [2]. We evaluate the performance of these algorithms by implementing them on the Xilinx Virtex-II pro [3], Virtex-5 [4] and Virtex-4 [6] FPGAs, by developing our own FFT processor architectures. Finally we show that the Grigoryan FFT is working faster than Cooley-Tukey FFT, consequently it is useful for higher sampling rates. At the same time we also confirm that Virtex-5 is better platform, for the same architectures, among all these for implementing Grigoryan FFT (FFT algorithm under evaluation), as Virtex-5 FPGAs give highest speed of operation for higher sampling rates of FFT. Operating at higher sampling rates is a challenge in DSP applications.

## Keywords

Frequency analysis, fast algorithms, DFT, FFT, paired transforms.

#### 1. Introduction

In the recent decades, fast orthogonal transforms have been widely used in areas of data compression, pattern recognition and image reconstruction, interpolation, linear filtering, and spectral analysis. The suitability of unitary transforms in each of the above applications depends on the properties of their basis functions as well as on the existence of fast algorithms, including parallel ones. Since the introduction of the Fast Fourier Transform (FFT), Fourier analysis has become one of the most frequently used tool in signal/image processing and communication systems; The main problem when calculating the transform relates to construction of the

DOI: 10.5121/ijma.2013.5407

<sup>&</sup>lt;sup>2</sup>Department of Electronics and Communications Engineering, Bharat Institute of Engineering and Technology, Hyderabad, A.P., India.

<sup>&</sup>lt;sup>3</sup>Department of Electronics and Communications Engineering, Vignan Institute of Technology and Science, Hyderabad, A.P., India.

decomposition, namely, the transition to the short DFT's with minimal computational complexity. The computation of unitary transforms is complicated and time consuming process. Since the decomposition of the DFT is not unique, it is natural to ask how to manage splitting and how to obtain the fastest algorithm of the DFT. The difference between the lower bound of arithmetical operations and the complexity of fast transform algorithms shows that it is possible to obtain FFT algorithms of various speed [2]. One approach is to design efficient manageable split algorithms. Indeed, many algorithms make different assumptions about the transform length. The signal/image processing related to engineering research becomes increasingly dependent on the development and implementation of the algorithms of orthogonal or non-orthogonal transforms and convolution operations in modern computer systems. The increasing importance of processing large vectors and parallel computing in many scientific and engineering applications require new ideas for designing super-efficient algorithms of the transforms and their implementations [2].

In this paper we present the implementation techniques and their results for two different fast DFT algorithms. The difference between the algorithm development lies in the way the two algorithms use the splitting of the DFT. The two fast algorithms considered are radix-2 Cooley-Tukey FFT and paired transform [2] based Grigoryan FFT algorithms. The implementation of the algorithms is done on the Xilinx Viretx-II Pro [3], Virtex-5 [4] and Virtex-4 [6] FPGAs. The performance of the two algorithms is compared in terms of their sampling rates and also in terms of their hardware resource utilization and also in terms of their percentage speed improvements. It is also discussed regarding their speed improvements for Virtex-5 and Virtex-4 over Virtex-II pro. Section 2 presents the paired transform decomposition used in the development of Grigoryan FFT. Section 3 presents the implementation techniques for the radix-2 (Cooley-Tukey FFT) and paired transform (Grigoryan FFT) algorithms on FPGAs. Section 4 presents the results. Finally with the Section 5 we conclude the work and put forward some suggestions for further sampling rate improvements.

# 2. DECOMPOSITION ALGORITHM OF THE FAST DFT USING PAIRED TRANSFORM

In this algorithm the decomposition of the DFT is done by using the *paired transform* [2]. Let  $\{x(n)\}$ , n = 0:(N-1) be an input signal, N>1. Then the DFT of the input sequence x(n) is

$$X(k) = \sum_{n=0}^{N-1} x(n)W_N^{nk}, k = 0:(N-1)$$

(1)

which is in matrix form

$$X = [F_N]x \tag{2}$$

where X(k) and x(n) are column vectors, the matrix  $F_N = \left\|W_N^{nk}\right\|_{n,k=(0:N-1)}$ , is a permutation of X.

$$F_{N} = dia\{[F_{N1}], [F_{N2}], \dots [F_{Nk}]\} \overline{[W]} [\chi_{N}]$$

(3)

which shows the applying transform is decomposed into short transforms  $F_{Ni}$ , i = 1: k. Let  $S_F$  be the domain of the transform F the set of sequences f over which F is defined. Let  $(D; \sigma)$  be a class of unitary transforms revealed by a partition  $\sigma$ . For any transform  $F \in (D; \sigma)$ , the

The International Journal of Multimedia & Its Applications (IJMA) Vol.5, No.4, August 2013 computation is performed by using paired transform in this particular algorithm. To denote this type of transform, we introduce "paired functions [2]."

Let  $p, t \in \text{period N}$ , and let

$$\chi_{p,t}(n) = \begin{cases} 1; np = t \pmod{N}; \\ 0; otherwise. \end{cases}$$

n = 0: (N-1) (4)

Let L be a non trivial factor of the number N, and  $W_L = e^{2\Pi/L}$ , then the complex function

$$\chi_{p,t}' = \chi_{p,t;L}' = \sum_{k=0}^{L-1} W_L^k \chi_{p,t+kN/l}$$

(5)

t = 0: (N/L-1), p $\in$  to the period 0: N-1

is called L-paired function [2]. Basing on this paired functions the complete system of paired functions can be constructed. The totality of the paired functions in the case of  $N=2^r$  is

{{

$$\chi_{2^{n}2^{n}t}}; t = 0: (2^{r-n-1}-1), n = 0: (r-1)$$

},1} (6)

Now considering the case of  $N = 2^r N_1$ , where  $N_1$  is odd,  $r \ge 1$  for the application of the paired transform.

- a) The totality of the partitions is  $\sigma' = (T_{1,2}, T_{2,2}, T_{4,2}, \dots, T_{2,2})$

- b) The splitting of  $F_N$  by the partition  $\sigma'$  is  $\{F_{N/2}, F_{N/4}, ....., F_{N/2^r}, F_{N1}\}$

- c) The matrix of the transform can be represented as

$$[F_N] = \left( \bigoplus [\overset{r}{F}_{Ln}] \right) [\overset{\longrightarrow}{W}] [\overset{\longrightarrow}{\mathcal{X}_n}]$$

$$L_n = N/2^{n+1}, L_r = N_1.$$

Where the [W] is diagonal matrix of the twiddle factors. The steps involved in finding the DFT using the paired transform are given below:

- 1) Perform the L-paired transform  $g = \chi_N(x)$  over the input x

- 2) Compose r vectors by dividing the set of outputs so that the first  $L^{r-1}$  elements  $g_1, g_2, \dots, g_L^{r-1}$  compose the first vector  $X_1$ , the next  $L^{r-2}$  elements  $g_{Lr-1}+1, \dots, g_{Lr-1+Lr-2}$  compose the second vector  $X_2$ , etc.

- 3) Calculate the new vectors  $Y_k$ , k=1:(r-1) by multiplying element-wise the vectors  $X_k$  by the corresponding turned factors  $1, W_t, W_t^2, ..., W_t^{t/L-1}, (t=L^{r-k})$ , (t=Lr-k). Take  $Y_r=X_r$

- 4) Perform the  $L_{r-k}$ -point DFT's over  $Y_k$ , k=1: r

- 5) Make the permutation of outputs, if needed.

# 3. IMPLEMENTATION TECHNIQUES

We have implemented various architectures for radix-2 and paired transform processors on Virtex-II Pro,Virtex-5 and Virtex-4 FPGAs. As there are embedded multipliers [3] and embedded block RAMs [3] available, we can use them without using distributed logic, which economize some of the CLBs [3]. Virtex-5 [4] is having DSP48E slices As we are having DSP48E slices on Virtex-5 FPGAs, to utilize them and improve speed performance of these 2 FFTs and to compare their speed performances on Virtex-5 FPGAs and Virtex-II pro FPGAs. We did the same for Virtex-4 FPGAs to observe the performance of both algorithms on Virtex-II pro and Virtex-4 by utilizing XtremeDSP slices. As most of the transforms are applied on complex data, the arithmetic unit always needs two data points at a time for each operand (real part and complex part), dualport RAMs are very useful in all these implementation techniques.

In the Fast Fourier Transform process the butterfly operation is the main unit on which the speed of the whole process of the FFT depends. So the faster the butterfly operation, the faster the FFT process. The adders and subtractors are implemented using the LUTs (distributed arithmetic). The inputs and outputs of all the arithmetic units can be registered or non-registered. Various possible implementations of multipliers we considered are:

## Embedded multiplier:

- a) With non-registered inputs and outputs

- b) With registered inputs or outputs, and

- c) With registered inputs and outputs.

Distributed multiplier: Distributed multipliers are implemented using the LUTs in the CLBs. These can also be implemented with the above three possible ways. Various considerations made to implement butterfly operation for its speed improvement and resource requirements. Basing on the availability of number of Embedded multipliers and design feasibility we have implemented both multiplication processes.

The various architectures proposed for implementing radix-2 and paired transform processors are single memory (pair) architecture, dual memory (pair) architecture and multiple memory (pair) architectures. We applied the following two best butterfly techniques for the implementation of the processors on the FPGAs [3].

- 1. One with Distributed multipliers, with fully pipelined stages. (Best in case of performance)

- 2. One with embedded multipliers and one level pipelining. (Best in case of resource utilization)

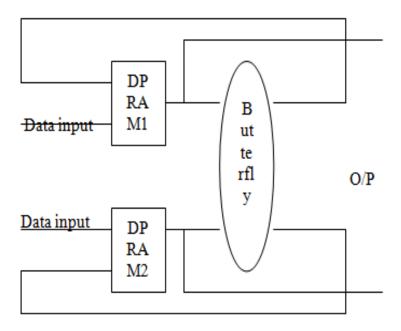

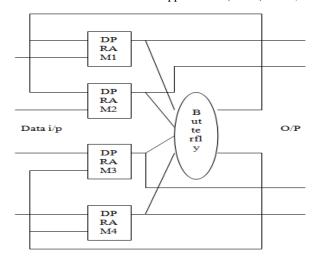

Single memory (pair) architecture (shown in Figure 1) is suitable for single snapshot applications, where samples are acquired and processed thereafter. The processing time is typically greater than the acquisition time. The main disadvantage in this architecture is while doing the transform process we cannot load the next coming data. We have to wait until the current data is processed. So we proposed dual memory (pair) architecture for faster sampling rate applications (shown in Figure 2). In this architecture there are three main processes for the transformation of the sampled data. Loading the sampled data into the memories, processing the loaded data, Reading out the processed data. As there are two pairs of dual port memories available, one pair can be used for loading the incoming sampled data, while at the same time the other pair can be used for processing the previously loaded sampled data. For further sampling rate improvements we proposed multiple memory (pair) architecture (shown in Figure 3). This is the best of all

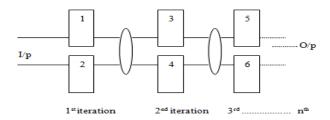

architectures in case of very high sampling rate applications, but in case of hardware utilization it uses lot more resources than any other architecture. In this model there is a memory set, one arithmetic unit for each iteration. The advantage of this model over the previous models is that we do not need to wait until the end of all iterations (i.e. whole FFT process), to take the next set of samples to get the FFT process to be started again. We just need to wait until the end of the first iteration and then load the memory with the next set of samples and start the process again. After the first iteration the processed data is transferred to the next set of RAMs, so the previous set of RAMs can be loaded with the next coming new data samples. This leads to the increased sampling rate.

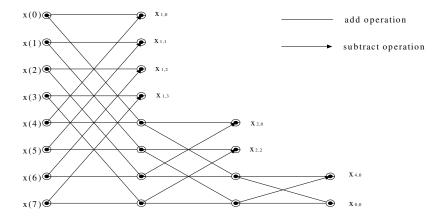

Coming to the implementation of the paired transform based DFT algorithm, there is no complete butterfly operation, as that in case of radix-2 algorithm. According to the mathematical description given in the Section 2, the arithmetic unit is divided into two parts, addition part and multiplication part. This makes the main difference between the two algorithms, which causes the process of the DFT completes earlier than the radix-2 algorithm. The addition part of the algorithm for 8-point transform is shown in Figure 4. The architectures are implemented for the 8-point 64-point,128-point,256-point transforms for Viretx-II Pro and Virex-5 and Virtex-4 FPGAs. The radix-2 FFT algorithm is efficient in case of resource utilization and the paired transform algorithm is very efficient in case of higher sampling rate applications.

Figure 1. Single memory (pair) architecture

The International Journal of Multimedia & Its Applications (IJMA) Vol.5, No.4, August 2013

Figure 2. Dual memory (pair) architecture

Figure 3. Multiple memory (pair) architecture (Transform length =  $N = 2^n$ )

(1,2);(3,4);(5,6) ---- (-,-) memory pairs for each iteration.

$\bigcap$  ----- Butterfly unit for each iteration.

Figure 4. Figure showing the addition part of the 8-point paired transform based DFT

# 3. THE IMPLEMENTATION RESULTS

Results obtained on Virtex-II Pro and Virtex-5 and Virtex-4 FPGAs: The hardware modeling of the algorithms is done by using Xilinx's system generator plug-in software tool running under SIMULINK environment provided under the Mathworks's MATLAB software. The functionality of the model is verified using the SIMULINK Simulator and the MODELSIM software as well. The implementation is done using the Xilinx project navigator backend software tools.

Table 1 shows the implementation results of the two algorithms on the Virtex-II Pro FPGAs. Table 2 shows the implementation results of the two algorithms on Virtex-5 FPGAs using DSP48E slices. Table 1 and 2 also show the percentage improvement in speed of Grigoryan FFT over Cooley-Tukey FFT. Table 3 shows the implementation results and percentage speed improvement in speed of Grigorayn FFT on Virtex-4 FPGAs using ExtremeDSP Slices. Table 4 shows the percentage improvement in speed of operation over Virtex-II Pro FPGAs, of Virtex-5 and Virtex-4; of both Cooley-Tukey and Grigoryan FFT algorithms.

From Tables 1, 2 and 3 we can see that Grigoryan FFT is always faster than the Cooley-Tukey FFT algorithm. Thus paired-transform based algorithm can be used for higher sampling rate applications. In military applications, while doing the process, only some of the DFT coefficients are needed at a time. For this type of applications paired transform can be used as it generates some of the coefficients earlier, and also it is very fast. But in terms of resource utilization Grigoryan FFT is utilizing more resources than Cooley-Tukey FFT, which makes Grigoryan FFT to be more expensive, but with higher speeds of operation. From Table 4 results we can easily verify that Grigoryan FFT can be utilized at higher sampling rates than Cooley-Tukey FFT. It is also clear that the high speed DSP slices are making the FFTs much faster than Virtex-II Pro FPGAs, both in case of Virtex-4 and Virtex-5 FPGAs. From the Table 4 we can also observe that for the same architectures the Virtex-5 platform is giving better speed of operation than Virtex-II pro and also on Virtex-4 FPGAs. So in the case of Grigoryan FFT, which is under performance evaluations in this research, it is preferable to choose Virtex-5 FPGA platforms.

Table 1. Efficient performance of Grigoryan FFT over Cooley-Tukey FFT, on Virtex-II Pro FPGAs. Table showing the sampling rates and the resource utilization summaries for both the algorithms, implemented on the Virtex-II Pro FPGAs.

| No. of points | Cooley-Tukey radix-<br>2 FFT |       |        | Grigoryan I | Radix-2 | % improvement In speed from Cooley-Tukey to Grigoryan FFT |       |

|---------------|------------------------------|-------|--------|-------------|---------|-----------------------------------------------------------|-------|

|               | Max.                         | No.   | No.    | Max.Freq.   | No.     | No.                                                       |       |

|               | freq.                        | of    | of     | MHz         | of      | of                                                        |       |

|               | MHz                          | mult. | Slices |             | mult    | slices                                                    |       |

| 8             | 35                           | 4     | 264    | 35          | 8       | 475                                                       | 0     |

| 64            | 42.45                        | 4     | 480    | 52.5        | 8       | 855                                                       | 23.67 |

| 128           | 50.25                        | 12    | 560    | 60          | 16      | 1248                                                      | 19.40 |

| 256           | 55.40                        | 24    | 648    | 68.75       | 48      | 1985                                                      | 24.09 |

The International Journal of Multimedia & Its Applications (IJMA) Vol.5, No.4, August 2013

Table 2. Efficient performance of Grigoryan FFT over Cooley-Tukey FFT, on Virtex-5 FPGAs. Table showing the sampling rates and the resource utilization summaries for both the algorithms, implemented on the Virtex-5 FPGAs. We have utilized DSP48E slices in this, which is making us much faster than Virtex-II Pro FPGAs.

| No. of points | Cooley-T<br>FFT      | Grigoryan Radix-2<br>FFT |                                |                                 | % improvement In speed from Cooley- Tukey to Grigoryan FFT |                                   |       |

|---------------|----------------------|--------------------------|--------------------------------|---------------------------------|------------------------------------------------------------|-----------------------------------|-------|

|               | Max.<br>freq.<br>MHz | No. of Slice s           | No. of<br>DSP48<br>E<br>slices | Ma<br>x.<br>fre<br>q<br>M<br>Hz | No. of Slice s                                             | No.o<br>f<br>DSP<br>48E<br>slices |       |

| 8             | 48                   | 200                      | 4                              | 52                              | 350                                                        | 4                                 | 8.33  |

| 64            | 55.25                | 375                      | 6                              | 60                              | 700                                                        | 8                                 | 8.59  |

| 128           | 60.50                | 450                      | 11                             | 80                              | 1000                                                       | 26                                | 32.23 |

| 256           | 75                   | 560                      | 14                             | 85                              | 1645                                                       | 82                                | 13.33 |

Table 3. Efficient performance of Grigoryan FFT over Cooley-Tukey FFT, on Virtex-4 FPGAs. Table showing the sampling rates and the resource utilization summaries for both the algorithms, implemented on the Virtex-4 FPGAs. We have utilized Extreme DSP slices in this, which is making us much faster than Virtex-II Pro FPGAs.

| No. of points | Cooley-Tukey radix-2<br>FFT |                          |                                        | Grigoryan Radix-2 FFT |                |                               | improvemen t In speed from Cooley- Tukey to Grigoryan FFT |

|---------------|-----------------------------|--------------------------|----------------------------------------|-----------------------|----------------|-------------------------------|-----------------------------------------------------------|

|               | Max.<br>freq.<br>MHz        | No.<br>of<br>Slic<br>-es | No. of<br>Extre<br>me<br>DSP<br>slices | Max.<br>freq<br>MHz   | No. of Slice s | No.of<br>DSP48<br>E<br>slices |                                                           |

| 8             | 41.38                       | 258                      | 4                                      | 50                    | 450            | 6                             | 20.83                                                     |

| 64            | 48                          | 400                      | 7                                      | 56.09                 | 800            | 8                             | 16.85                                                     |

| 128           | 53                          | 496                      | 12                                     | 72                    | 1120           | 28                            | 35.85                                                     |

| 256           | 67                          | 598                      | 20                                     | 79.95                 | 1735           | 86                            | 19.33                                                     |

The International Journal of Multimedia & Its Applications (IJMA) Vol.5, No.4, August 2013

Table 4. The percentage improvement in speed of operation over Virtex-II Pro FPGAs, of Virtex-5 and Virtex-4; of both Cooley-Tukey and Grigoryan FFT algorithms. It shows clearly that Virtex-5 plat form is better than Virtex-4 and also Virtex-II pro, in terms of speed of operation.

| Number<br>Of<br>Sample<br>points<br>of FFT | % Improvement in speed over Xilinx Virtex-II Pro FPGAs |            |               |            |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------|------------|---------------|------------|--|--|--|--|

|                                            | Cooley-Tukey FFT                                       |            | Grigoryan FFT |            |  |  |  |  |

|                                            | Virtex - 5                                             | Virtex - 4 | Virtex - 5    | Virtex - 4 |  |  |  |  |

| 8                                          | 37.14                                                  | 18.23      | 48.57         | 42.86      |  |  |  |  |

| 64                                         | 30.15                                                  | 13.07      | 14.29         | 6.84       |  |  |  |  |

| 128                                        | 20.40                                                  | 5.47       | 33.33         | 20         |  |  |  |  |

| 256                                        | 35.38                                                  | 20.94      | 23.64         | 16.29      |  |  |  |  |

#### 4. CONCLUSIONS AND FURTHER RESEARCH

In this paper we have shown that on Virtex-II Pro, Virtex-5 and Virtex-4 FPGAs the paired transform based Grigoryan FFT algorithm is faster and can be used at higher sampling rates than the Cooley-Tukey FFT at an expense of high resource utilization. Grigoryan FFT and also Cooley-Tukey FFT both are running at higher speeds on Virtex-5 platform. So we ultimately recommend these implementations to be done onto Virtex-5 FPGAs than onto any other FPGAs.

We are planning to implement these algorithms onto Latest TMS DSP processors, and also by utilizing MAC engines on them; for extensive verification of these two FFT algorithms. Then we would like to standardize Grigoryan FFT and apply for real time applications.

#### ACKNOWLEDGEMENTS

This is to thank Dr. Parimal A. Patel, Dr. Artyom M. Grigoryan of The University of Texas at San Antonio; regarding their valuable guidance to do the first part of this research series as my (Mr. Narayanam) master's thesis. Their support will always be with me to make Grigoryan FFT as a standarad FFT as our patent in the industrial market. I would like to thank also University of Ottawa research facility providers to provide me to do some critical part of this extended research.

## REFERENCES

- [1] James W. Cooley and John W. Tukey, "An algorithm for the machine calculation of complex Fourier Series", Math. comput. 19, 297-301 (1965).

- [2] Artyom M. Grigoryan and Sos S. Agaian, "Split Manageable Efficient Algorithm for Fourier and Hadamard transforms", IEEE Transactions on Signal Processing, Volume: 48, Issue: 1, Pages: 172 183, Jan.2000.

- [3] Virtex-II Pro platform FPGAs: detailed description http://www.xilinx.com/support/documentation/data\_sheets/ds083.pdf

- [4] Virtex-5 platform FPGAs: detailed description http://www.xilinx.com/support/documentation/virtex-5\_user\_guides.htm

- [5] N. Ranganadh, P. Patel, and A.M. Grigoryan, "Case study of Grigoryan FFT onto FPGAs and DSPs", IEEE proceedings, IEEE ICECT 2012, 2012 4th International Conference on Electronics Computer Technology (ICECT 2012), kanya kumari 2012.

- [6] Virtex-4 platform FPGAs: detailed description http://www.xilinx.com/support/documentation/virtex-4\_user\_guides.htm

- [7] The scientist and engineer's guide to Digital Signal Processing, Dr. Steven W. Smith.

- The International Journal of Multimedia & Its Applications (IJMA) Vol.5, No.4, August 2013

- [8] N. Ranganadh, P. Patel, and A.M. Grigoryan, "Implementation of the DFT using radix-2 and paired transform algorithms," 17th International Conference on Computer Applications in Industry and Engineering, CAINE-2004, Orlando, Florida USA, Nov. 17-19, 2004.

- [9] N. Ranganadh, P. Patel, and A.M. Grigoryan, "performances of Texas instruments DSP and Xilinx FPGAs for Cooley-Tukey and Grigoryan FFT algorithms", Wolters Kluwer and Medknow International Journal of Engineering and Technology, Jul-Dec 2011, Vol 1, Issue 2.

#### Authors

Mr. Ranganadh Narayanam is an Assistant professor in the department of Electronics & Communications Engineering in Bharat Institute of Engineering & Technology (BIET). This research is continuation of the research done in the University of Texas at San Antonio under the guidance of Dr. Parimal A. Patel, Dr. Artyom M. Grigoryan, as my master's thesis. This current research was partly funded by BIET. Mr.Narayanam, a research student in the area of "Brain Stem Speech Evoked Potentials" under the guidance of Dr. Hilmi Dajani of University of Ottawa, Canada. He was also a research student in The University of Texas at San Antonio under Dr. Parimal A Patel, Dr. Artyom M. Grigoryan, Dr Sos Again, Dr. CJ Qian,. in the areas of signal processing and digital systems, control systems. He worked in the area of Brian Imaging in University of California Berkeley. Mr. Narayanam is having around 5+2 years of full time teaching & research experiences respectively; and more than 5 years of entry level research experience and more than 15 publications. Mr. Narayanam's research interests include neurological Signal & Image processing, DSP software & Hardware design and implementations, neurotechnologies. Mr. Narayanam was a TPGFS grant holder Through The University of Texas at San Antonio for the year 2003 to 2004. Mr. Narayanam can also be contacted at rnara100@uottawa.ca, rnara100@gmail.com, rnara100@biet.ac.in, ranganadh.narayanam@gmail.com

**Mr. P. Muni Guravaiah** is an Associate Professor & Admin. Incharge of Department of Electronics & Communications Engineering in BIET. He is currently pursuing Ph.D. in Jawaharlal Nehru Technological University Hyderabad, in the area of VLSI Design. His research interests include DSP; VLSI Design. He is having around 12-15 years of accumulated Teaching and Research experiences.

Ms. Bindu Tushara D. is currently an Assistant Professor in Vignan Institute of Technology & Science (VITS). She is a double gold medalist of Jawaharlal Nehru Technological University as the best out going student of the year 2009. She has received medals from Governer of Andhara Pradesh. Her research interests are DSP and Wireless Communications.